DDRxシミュレーション

シミュレーションの難しさ

- 引き回し密度が高く、粒子数が多く、運転速度が高く、タイミングマージンが小さく、駆動の種類が多い

シミュレーションの目的

- Layoutの配置配線の指導

- プロジェクトのデバッグに問題があり、シミュレーションを通じて問題を特定し、改善のための提案を行います

- チップ内部の信号は測定できず、外部テストデータをシミュレーションで比較し、チップ内部の実際の状態を解析します

シミュレーション 内容

- トポロジー最適化、ODT調整、駆動選択、終端/ストリング抵抗値調整、タイミング解析、すべての信号線のフルチャネルシミュレーション

シミュレーションの意味

- Layoutの配置配線の指導

- (LP)DDR3/4/5、GDDR6 トポロジ タイプの選択

- 低消費電力要求時にODTをオフにしても動作するか

- (LP)DDR3/4/5、GDDR6は、高密度で、コスト削減(例えば、レイヤー削減、通常のプロセスを使用)時の設計指導

- HDI設計時に、完全な参照平面がない、または十分な等長条件が得られない場合に与えられる配線ガイド

シミュレーション対象

DDR(LPDDR)3/4/5フルチャンネルシミュレーション

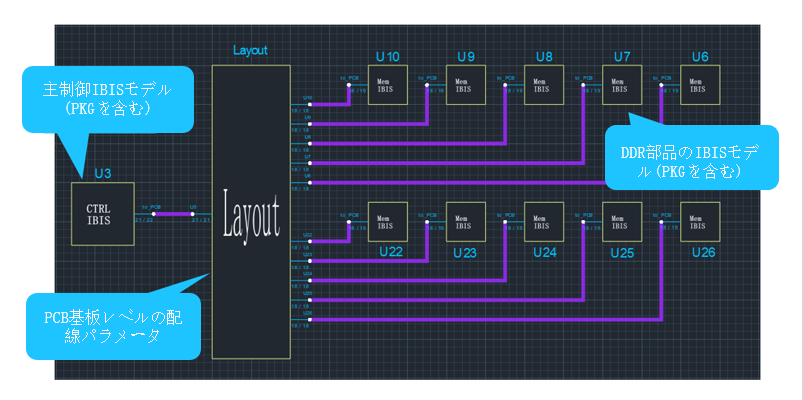

ある国産のCPUチップ DDR5の1対10トポロジーオンボード全チャネルシミュレーション実績

ある国産のCPU-DDR5の全チャネルシミュレーション実績

設計経験

年間15,000以上の設計経験を持ち、業界をリードするDDRシミュレーション技術を構築しています

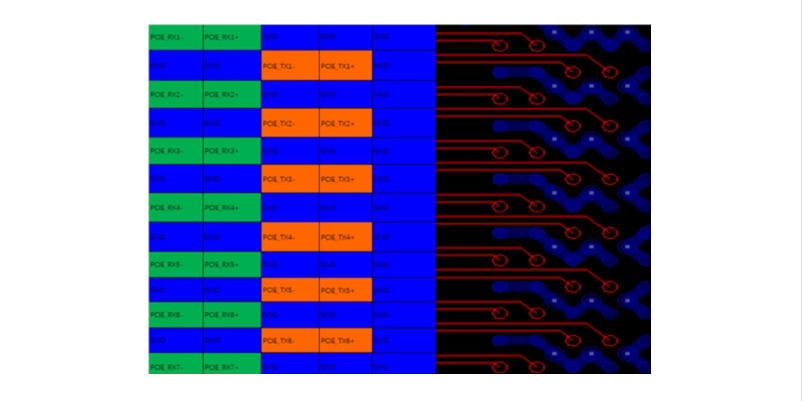

以下の写真は、近年人気のAI人工知能の加速カード設計であり、難易度の高い設計とシミュレーションは内外のAI会社がその製品を迅速に発売するのを助けます

最大6400Mbpsの動作速度を持つ高密度マルチチャネルLPDDR5パワーカード

シミュレーション 内容

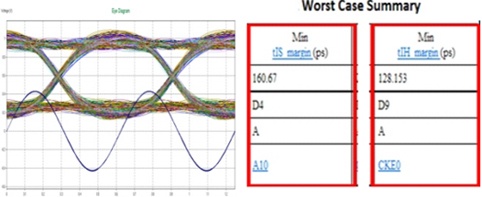

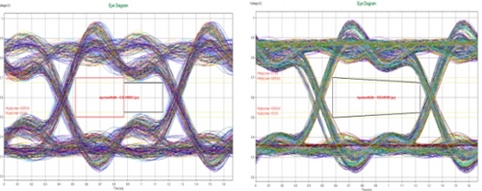

信号品質シミュレーション:

-シミュレーションの最適化前後の結果の比較

信号タイミングシミュレーション:

-各グループの信号タイミング関係対応

-時系列ウィンドウの計算 (時間 Margin の確立/保持)